# DATASHEET PIM400 Series; ATCA Board Power Input Modules

-36 to -75 Vdc; 400W/10A

9Vdc - 36Vdc input; +15V, -15V Dual Output, 0.3A 9W Output

### **Applications**

- ATCA Front Board / Blade

- Central Office Telecom equipment

- High availability server and storage applications

### **Features**

- -48V/10A Dual redundant input power distribution

- 3.3Vdc/3.6A & 5.0Vdc/150mA of isolated Management Power for IPM or other housekeeping functions

- Independent holdup capacitor charging voltage; trimmable from 50 to 95Vdc for optimal real estate

- OR'ing functionality, Inrush protection & hot swap capability

- Integral EMI filter designed for the ATCA board to meet CISPR Class B with minimal external filtering

- Protection: Reverse polarity, under voltage, input transient over voltage/current and temperature

- I<sup>2</sup>C digital interface options

- Isolated A/B Feed Loss /Open Fuse Alarm

- High efficiency : 98%

See Footnote on Page No. 6

### Description

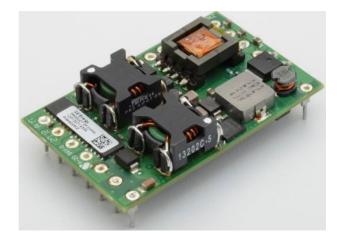

The PIM400 series of Power Input Modules are designed to greatly simplify the task of implementing dual redundant, hot swap -48Vdc power distribution with EMI filtering on an ATCA or other telecom boards. The PIM400 with optional I<sup>2</sup>C digital interface capability, when used with a variety of OmniOn's series of Bus converters (Barracuda<sup>™</sup> Series) /POLs (DLynx<sup>™</sup> Series) provides for a quick, simple and elegant power solution to a wide variety of demanding & intelligent power system architectures.

### Options

- Choice of short pin lengths

- I<sup>2</sup>C Digital Interface

- - 40 to 85°C ambient temperature operation

- Industry Standard Quarter brick size: 58.4 mm x 36.8 mm x 13.7 mm (2.3 in x 1.45 in x 0.54 in)

- MTBF : 2,308,563 hours per TELCORDIA

- Compliant to RoHS Directive 2011/65/EU and amended Directive (EU) 2015/863

- Compliant to REACH Directive (EC) No 1907/2006

- ANSI/UL# 62368-1 and CAN/CSA† C22.2 No. 62368-1 Recognized, DIN VDE‡ 0868-1/A11:2017 (EN62368-1:2014/A11:2017)

- Meets the voltage and current requirements for ETSI 300-132-2 and complies with and licensed for Basic insulation rating 2250 Vdc Isolation tested in compliance with IEEE 802.3¤ PoE standards

- ISO\*\*9001 and ISO 14001 certified manufacturing facilities

# **Technical Specifications**

### **Absolute Maximum Ratings**

Stresses in excess of the absolute maximum ratings can cause permanent damage to the device. These are absolute stress ratings only, functional operation of the device is not implied at these or any other conditions in excess of those given in the operations sections of the data sheet. Exposure to absolute maximum ratings for extended periods can adversely affect the device reliability.

| Parameter                                                                                              | Device | Symbol         | Min  | Тур | Max  | Unit            |

|--------------------------------------------------------------------------------------------------------|--------|----------------|------|-----|------|-----------------|

| Input Voltage                                                                                          |        |                |      |     |      |                 |

| Continuous                                                                                             | All    | VI             | -0.5 |     | -75  | V <sub>dc</sub> |

| Transient (Pulse duration = 1ms, square wave)                                                          | All    | Vtr            |      |     | -100 | $V_{dc}$        |

| Additionally: Transient Input Undervoltage,<br>Overvoltage and Impulse per ANSI TI.315-2001<br>(R2006) | All    |                |      |     |      |                 |

| Reverse Polarity Protection                                                                            |        |                |      |     | +75V | $V_{dc}$        |

| Holdup Capacitor                                                                                       |        |                |      |     |      |                 |

| Voltage (with respect to -48V_OUT)                                                                     | All    | V_HLDP         | 100  |     | 100  | $V_{dc}$        |

| Capacitance                                                                                            | All    | C_HLDP         | 100  |     | 3300 | μF              |

| Temperature                                                                                            |        |                |      |     |      |                 |

| Normal Operating Ambient Temperature (See<br>Thermal Considerations section)                           | All    | T <sub>A</sub> | -40  |     | 85   | °C              |

| Storage Temperature                                                                                    | All    | $T_{stg}$      | -55  |     | 125  | °C              |

| Isolation Voltage                                                                                      |        |                |      |     |      |                 |

| Input to MGMT_PWR Output Voltage & Alarm                                                               | All    |                |      |     | 2250 | V <sub>dc</sub> |

| Input to SHELF_GND Voltage                                                                             | All    |                |      |     | 2250 | $V_{dc}$        |

| Input to LOGIC_GND Voltage                                                                             | All    |                |      |     | 2250 | V <sub>dc</sub> |

#### CAUTION:

1. This power module is not internally fused. Both A & B feeds and their corresponding returns must be individually fused.

To preserve maximum flexibility, internal fusing is not included. However, to achieve maximum safety and system protection, the safety agencies require a fast-acting fuse with a maximum rating of 20 Amps and Voltage Rating >/= 75Vdc for the -48AF, -48BF VRTN\_AF & VRTN\_BF feeds. Consult Fusing and fault protection Section of PICMG 3.0 ATCA specifications for additional information. Based on the information provided in this data sheet on inrush

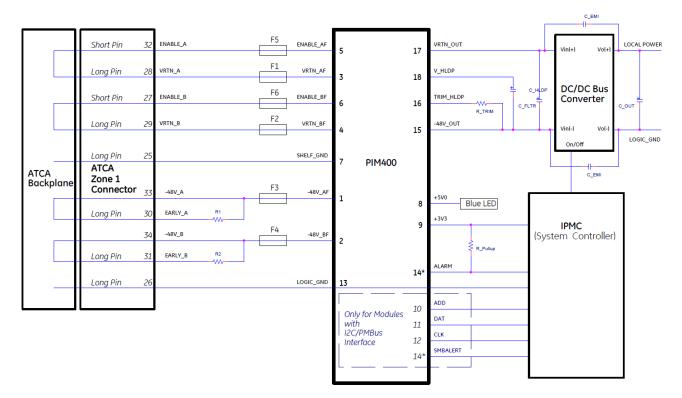

### ATCA Board Typical Application

| External Holdup Capacitor Selection                      | External Holdup Trim Resistor Selection                     |

|----------------------------------------------------------|-------------------------------------------------------------|

| $C_{HLDP} = \frac{2T_{HU}P_{HU}}{V_{HLDP^2} - V_{UV}^2}$ | $R_TRIM(\Omega) = (\frac{500,000}{V_HLDP - 50.0} - 10,000)$ |

### **Suggested Bill of Materials**

(Note: Customer is ultimately responsible for the final selection and verification of the suggested parts for the end application).

| <b>Ref Des</b> | Description (Values)           | Comments                                                        |

|----------------|--------------------------------|-----------------------------------------------------------------|

| F1-F4          | Fuses (15A)                    | Max fuse rating not to exceed 20A, fast acting                  |

| F5,F6          | Fuses (15A)                    | 0.5 to 1A rated                                                 |

| R1,R2          | Pre-charge Resistors (15 Ohms) | High Surge Power Type e.g. KOA P/N SG73                         |

| R_TRIM         | Resistor                       | See Design Consideration section for details                    |

| R_PULLUP       | Resistor (3.3 kOhms)           | Alarm pull-up resistor                                          |

| C_FLTR         | Capacitor(s) (100µF)           | 300 µF (max)                                                    |

| C_HLDP         | Capacitor(s)                   | $3300\mu$ F (max); see Design Consideration section for details |

| C_OUT          | Capacitor(s)                   | Consult data sheet for the applicable DC/DC Bus Converter       |

| C_EMI          | Capacitors                     | See Design Consideration section for details                    |

See Footnote on Page No. 6 Page 3

**Electrical Specifications** Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions.

| Parameter                                                                                                                                                                                                                              | Device     | Symbol                                            | Min            | Тур            | Max            | Unit       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------|----------------|----------------|----------------|------------|

| -48V Dual Feed Inputs (-48_AF,-48_BF,VRTN_AF,VI                                                                                                                                                                                        | RTN_BF)    |                                                   |                |                |                |            |

| Input Voltage Range                                                                                                                                                                                                                    | All        | VI                                                | -36            | -48            | -75            | Vdc        |

| Output Current<br>With the following maximum power limits<br>400W @ 40Vin, 480W @ 48Vin, 540W @ 54Vin                                                                                                                                  | All        | I,                                                |                |                | 10             | Adc        |

| Disabled input current drain if input voltage falls<br>below V <sub>UVLO</sub> for > 2 seconds.                                                                                                                                        | All        | I <sub>UVLO</sub>                                 |                | 10             |                | mA         |

| Enabled No-load input current                                                                                                                                                                                                          | All        | I <sub>stdby</sub>                                |                | 40             | 70             | mΑ         |

| Inrush Transient<br>(@ -48 VI, C_FLTR = 200µF & EARLY_A, EARLY_B Pre<br>-chargeresistors 15 ohms per leg as recommended<br>in the "ATCA Board Typical Application" figure, p=2)<br>Duration: 0.1ms to 0.9ms<br>Duration: 0.9ms to 3 ms | All        | lpk                                               |                |                | 40             | Adc        |

| (Logarithmically declining)                                                                                                                                                                                                            |            | lpk                                               |                |                | 40 to 18       | Adc        |

| ENABLE A/B Signal Inputs (ENABLE_A, ENABLE_B)                                                                                                                                                                                          |            |                                                   |                |                |                |            |

| Input Voltage Threshold (On/Off); Default Setting                                                                                                                                                                                      | All        | V <sub>UVHI</sub> (On)<br>V <sub>UVLO</sub> (Off) | -33.5<br>-32.4 | -35.3<br>-33.7 | -36.0<br>-34.1 | Vdc        |

| Enable A / B Signals current drain (Vin = -48Vdc)                                                                                                                                                                                      | All        |                                                   |                | 380            |                | µAdc       |

| Main Output (-48V_OUT, VRTN_OUT)                                                                                                                                                                                                       |            |                                                   |                |                |                |            |

| Efficiency (Vin=-48V; 3,3V/5.0V @ no load)<br>400W Output Power<br>300W Output Power                                                                                                                                                   | All<br>All | η<br>η                                            |                | 98.2<br>98.5   |                | %          |

| Output Voltage Delay                                                                                                                                                                                                                   | All        | T <sub>delay</sub>                                |                | 100            |                | ms         |

| Input Current Limit                                                                                                                                                                                                                    | All        | l <sub>limit</sub>                                | 11             | 13             | 15             | А          |

| External Output Filter Capacitance (C_FLTR)                                                                                                                                                                                            | All        | C_FLTR                                            | 80             | 100            | 300            | μF         |

| Holdup Capacitor Output Voltage (V_HLDP)                                                                                                                                                                                               |            |                                                   |                |                |                |            |

| Holdup Capacitor Voltage Trim Range                                                                                                                                                                                                    |            | V_HLDP                                            | 50             | 90             | 95             | V          |

| Holdup Capacitor Output Voltage Tolerance<br>@V_HLDP=90Vdc<br>(2)( OUT Thread ald                                                                                                                                                      |            |                                                   | +6             |                | -6             | %          |

| -48V_OUT Threshold<br>To charge external holdup capacitors (C_HLDP)<br>To discharge external holdup capacitors (C_HLDP)                                                                                                                | All        |                                                   |                | 40.0<br>-36.0  |                |            |

|                                                                                                                                                                                                                                        |            |                                                   |                |                |                | ) //ma.a   |

| dV/dt on Hold-up Connect<br>Switching Frequency                                                                                                                                                                                        |            | f                                                 |                | 80             |                | V/ms       |

| A/B Feed Loss / Fuse Alarm Output (ALARM)                                                                                                                                                                                              |            | 1                                                 | 1              | 330            | I              | kHz        |

| ALARM ON Input Voltage Threshold<br>ALARM OFF Input Voltage Threshold                                                                                                                                                                  | All        |                                                   | -36.4          | -37.2<br>-40.5 | -40.4          | Vdc<br>Vdc |

| External Pull-up Voltage                                                                                                                                                                                                               | All        |                                                   |                |                | 5.0            | Vdc        |

| L                                                                                                                                                                                                                                      |            |                                                   | I              | 1              | 1              |            |

See Footnote on Page No. 6

## **Electrical Specifications** (Continued)

| Parameter                                                                                                                                                                          | Output<br>Voltage | Symbol                               | Min   | Тур            | Max       | Unit                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------|-------|----------------|-----------|-------------------------|

| +3.3V Isolated Management Power Output (+3V                                                                                                                                        | /3)               |                                      |       |                |           |                         |

| Input Under-Voltage Lockout<br>Turn-On Voltage Threshold                                                                                                                           | All               |                                      | -32.4 | -33.7<br>-34.5 | -34.1     | V<br>V                  |

| Total Output Voltage Range<br>(Over all operating input voltage, resistive Load<br>and temperature conditions until end of life).                                                  | All               | +3V3                                 | 3.170 | 3.350          | 3.430     | V                       |

| Output Current                                                                                                                                                                     | All               | Ιo                                   | 0     | -              | 3.6       | Adc                     |

| Output Ripple and Noise<br>Measured across 10µF ceramic capacitor<br>VI = VI,nom TA = 25°C, Io = Io,max<br>RMS (500 MHz bandwidth)<br>Peak-to-peak (500MHz bandwidth)              | All               |                                      | -     | 16<br>75       | 50<br>200 | mVrms<br>mVp-p          |

| Output Current- Limit Inception                                                                                                                                                    | All               | I <sub>o,lim</sub>                   | -     | 4              | 6         | Arms                    |

| Output Short-circuit Current                                                                                                                                                       | All               | I <sub>o,sc</sub>                    | -     | 3              | -         | Arms                    |

| External Load Capacitance                                                                                                                                                          | All               | C <sub>O,max</sub>                   | 0     | -              | 1000      | μF                      |

| Switching Frequency                                                                                                                                                                | All               | f                                    |       | 330            |           | kHz                     |

| Dynamic Response<br>(di/dt =0.1A/µs, V <sub>lin</sub> = V <sub>in,nom</sub> , T <sub>A</sub> =25°C)<br>Load change from IO = 50% to 75% of I <sub>O, max</sub> ,<br>Peak Deviation | All               | V <sub>pk</sub>                      |       | 7              |           | %, V <sub>O</sub> , set |

| Settling Time (V <sub>0</sub> <10% of peak deviation)<br>Turn-On Delay                                                                                                             | All               | t <sub>s</sub><br>T <sub>delay</sub> |       | 800<br>50      |           | μs<br>μ                 |

| (Io = 80% of Io,max, T <sub>A</sub> =25°C)<br>Output voltage overshoot<br>(Io = 80% of Io,max, VI = 48Vdc TA=25°C)                                                                 | All               | l delay                              |       |                | 3%        | , V <sub>O, set</sub>   |

| Output Over Voltage Protection                                                                                                                                                     | All               | V <sub>o, limit</sub>                | 3.7   |                | 5.4       | V                       |

| +5.0V Isolated Management Power Output (+5V0)                                                                                                                                      | )                 |                                      |       | •              |           |                         |

| Total Output Voltage Range<br>(Over all operating input voltage, resistive Load<br>and temperature conditions until end of life).                                                  | All               | +5V0                                 | 4.80  | 5.00           | 5.20      | V                       |

| Output Current                                                                                                                                                                     | All               | I <sub>o</sub>                       | 0     | -              | 150       | mAdc                    |

| Output Current-Limit Inception                                                                                                                                                     | All               | I <sub>o,lim</sub>                   | -     | 250            | -         | mA                      |

| Output Short-circuit Current                                                                                                                                                       | All               | I <sub>o,sc</sub>                    | -     | 150            | -         | mA <sub>RMS</sub>       |

| External Load Capacitance                                                                                                                                                          | All               | C <sub>O,max</sub>                   | 0     | -              | 1000      | μF                      |

| Switching Frequency                                                                                                                                                                | All               | f                                    | -     | 330            | -         | kHz                     |

### **Digital Interface Specifications**

Unless otherwise indicated, specifications apply over all operating input voltage, resistive load, and temperature conditions. See Feature Descriptions for additional information.

| Parameter                                | Conditions  | Symbol           | Min | Тур  | Max | Unit |

|------------------------------------------|-------------|------------------|-----|------|-----|------|

| Digital Signal Interface Characteristics |             |                  |     |      |     |      |

| Clock frequency range                    |             | f <sub>CLK</sub> |     | 100  | 400 | kHz  |

| Measurement Tolerance                    |             |                  |     |      |     |      |

| Feed Voltage A/B (-48V_AF & -48V_BF)     |             |                  |     | +/-3 |     | %    |

| Holdup Voltage (V_HLDP)                  |             |                  |     | +/-3 |     | %    |

| -48V_OUT current (-48V_IOUT)             | % of lo,max |                  |     | +/-3 |     | %    |

| Module Temperature (TEMP)                |             |                  |     | +/-3 |     | °C   |

### **General Specifications**

| Parameter                                                                       | Device | Min | Тур        | Max | Unit    |

|---------------------------------------------------------------------------------|--------|-----|------------|-----|---------|

| Calculated MTBF (Po=0.8Po, <sub>RATED,</sub> 48Vin, Ta=40°C,<br>Airflow=300LFM) | All    |     | 2,308,563  |     | Hours   |

| Telecordia Issue 2 Method 1 Case 3                                              |        |     |            |     |         |

| Weight                                                                          |        | -   | 28.3 (1.0) | -   | g (oz.) |

FOOTNOTES

UL is a registered trademark of Underwriters Laboratories, Inc.

† CSA is a registered trademark of Canadian Standards Association.

<sup>+</sup> VDE is a trademark of Verband Deutscher Elektrotechniker e.V. \*\* ISO is a registered trademark of the International Organization of Standards

¤ IEEE and 802 are registered trademarks of the Institute of Electrical and Electronics Engineers, Incorporated.

### **Characteristic Curves**

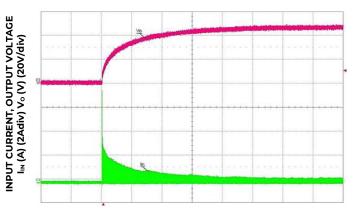

The following figures provide typical characteristics for the PIM400X modules at 25°C.

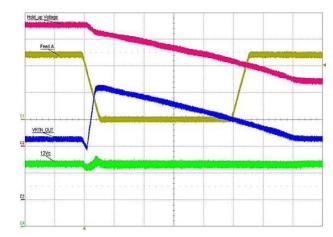

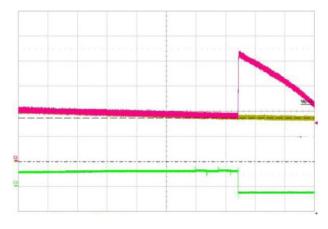

TIME, t (2ms/div)

Test Conditions: 48Vin, 400W, C\_FLTR = 100uF

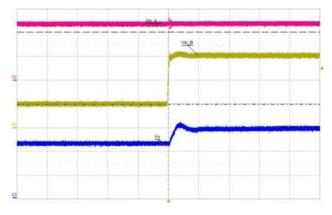

TIME, t (200µs/div)

Fig 2: Input Transient on one feed CH1: Feed B step to 60V (20V/Div) CH2: Feed A at 48V (20V/Div) CH3: VRTN\_OUT (20V/Div)

> Test Conditions: Full load

TIME, t (2ms/div)

Fig 4: Hold-up Event vs 12.0Vout CH1: Feed A (20V/Div) CH2: Hold-up Voltage (20V/Div) CH3: VRTN\_OUT (20V/Div) CH4: 12.0 Vout (5V/Div)

Test Conditions: 1. Payload Bus Converter: QBVW033A0B 2. Load: 12.0V Bus Converter Output @ 33A; 3.3V@3.6A 3. C\_Hold-up = 2200 µF 4. C\_FLTR=220µF 5. V\_HLDP=90V

TIME, t (2ms/div)

Fig 3: Hold-up Event vs 3.3Vout CH1: Feed A (20V/Div) CH2: Hold-up Voltage (20V/Div) CH3: VRTN\_OUT (20V/Div) CH4: 3.3Vout (2V/Div)

Test Conditions: 1. Payload Bus Converter: QBVW033A0B 2. Load: 12.0V Bus Converter Output @ 33A; 3.3V@3.6A 3. C\_Hold-up = 2200 µF 4. C\_FLTR=220µF 5. V\_HLDP=90V

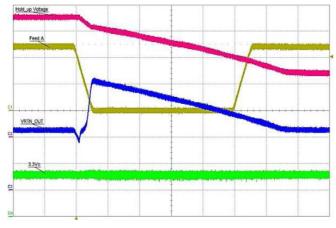

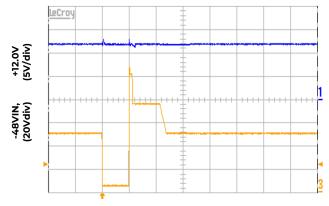

### Characteristic Curves (continued)

The following figures provide typical characteristics for the PIM400X modules at 25°C.

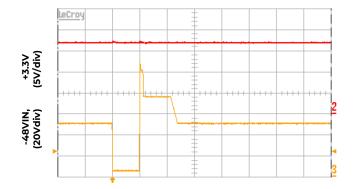

TIME, t (20ms/div)

Fig 5: Turn- ON Threshold

CH1: Input Voltage (20V/Div) CH2: VRTN\_OUT voltage (20V/Div) CH4: Input Current (5A/Div)

TIME, t (10ms/div)

Fig 7a: Line Transient performance per ANSI TI.315-2001 standard vs +12.0V output

CH1: +12Voutput voltage (5V/Div) CH3: -48V input Voltage (20V/Div) Test Conditions:

1. PIM400 + QBDW033A0 (12V Bus Converter)

- 2. Load: +12Vout @ 30A; 3.3V @ 3.0A 3. C\_HLDP = 2200 µF

- 4. C\_FLTR) = 220 μF

TIME, t (10ms/div)

Fig 6: Turn- OFF Threshold

CH1: Input Voltage (20V/Div) CH2: VRTN\_OUT voltage (20V/Div) CH4: Input Current (2A/Div)

#### TIME, t (10ms/div)

Fig 7b: Line Transient performance per ANSI TI.315-2001 standard vs 3.3V output

CH2: +3V3 Output Voltage (IV/Div) CH3: -48V input Voltage (20V/Div) Test Conditions: 5. PIM400 + QBDW033A0 (12V Bus Converter) 6. Load: +12Vout @ 30A; 3.3V @ 3.0A 7. C\_HLDP = 2200 µF

8. C\_FLTR) = 220 μF

10

10

# Technical Specifications (continued)

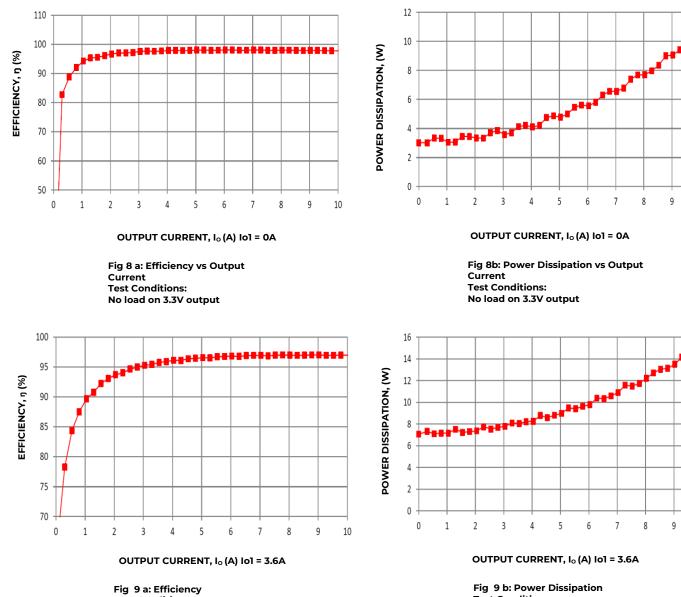

### Characteristic Curves (continued)

The following figures provide typical characteristics for the PIM400X modules at 25°C.

Test Conditions: Full load on 3.3V output Fig 9 b: Power Dissipation Test Conditions: Full load on 3.3V output

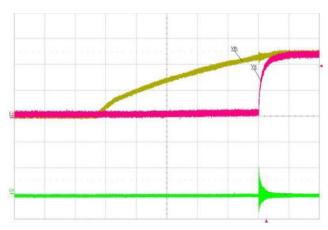

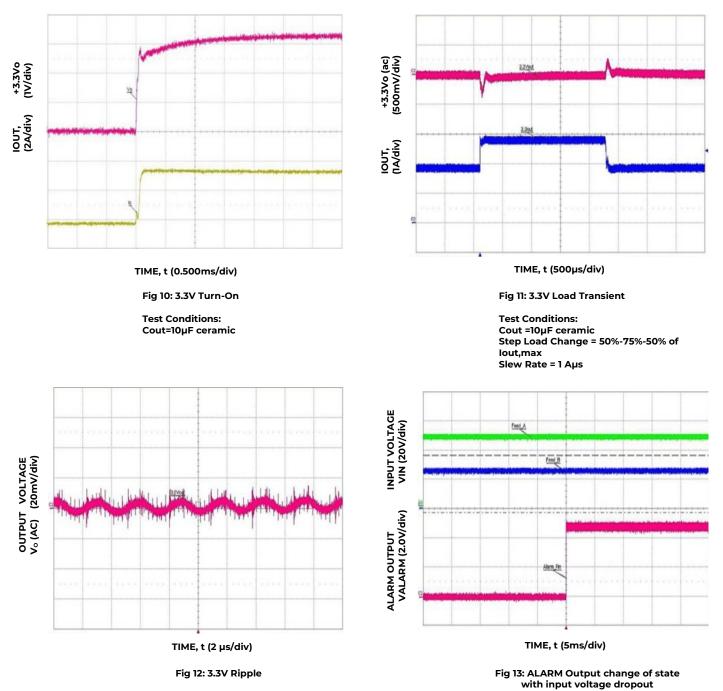

### Characteristic Curves (continued)

The following figures provide typical characteristics for the PIM400X modules at 25°C.

Test Conditions: Cout=10µF ceramic Iout=3.6A

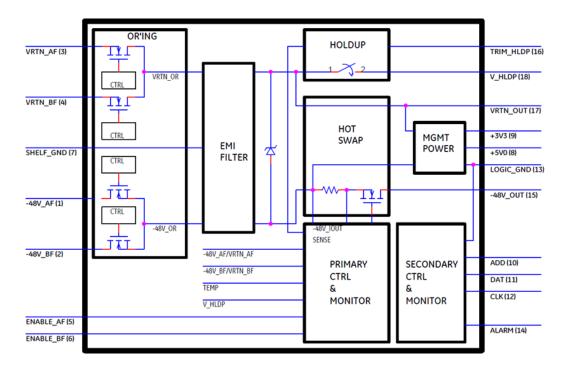

### PIM400 Internal Block Diagram

### **PIN FUNCTIONS**

| Pin No. | Signal Name | Description                                                                            |

|---------|-------------|----------------------------------------------------------------------------------------|

| 1       | -48V_AF     | -48V_A Feed (Externally Fused)                                                         |

| 2       | -48V_BF     | -48V_B Feed (Externally Fused)                                                         |

| 3       | VRTN_AF     | VRTN_A Feed (Externally Fused)                                                         |

| 4       | VRTN_BF     | VRTN_B Feed (Externally Fused)                                                         |

| 5       | ENABLE_AF   | ENABLE_A Feed (Externally Fused)<br>(Short Pin, connected to VRTN_A on the back plane) |

| 6       | ENABLE_BF   | ENABLE_B Feed (Externally Fused)<br>(Short Pin, connected to VRTN_B on the back plane) |

| 7       | SHELF_GND   | Shelf / Chassis / Safety Ground                                                        |

| 8       | +5V0        | Isolated 5.0Vdc (Blue LED Power) w.r.t. LOGIC_GND                                      |

| 9       | +3V3        | Isolated 3.3Vdc (Management Power) w.r.t. LOGIC_GND                                    |

| 10**    | ADD         | I2C Address w.r.t. LOGIC_GND                                                           |

| 11**    | DAT         | I2C Data w.r.t. LOGIC_GND                                                              |

| 12**    | CLK         | I2C Clock w.r.t. LOGIC_GND                                                             |

| 13      | LOGIC_GND   | Logic / Secondary / Isolated Ground                                                    |

| 14      | ALARM       | Opto-isolated -48V A/B Feed Loss or Open Fuse Alarm (w.r.t LOGIC_GND)                  |

| 15      | -48V_OUT    | OR'd and Inrush protected –48V Output Bus                                              |

| 16      | TRIM_HLDP   | Holdup capacitor output voltage trim w.r.t48V_OUT                                      |

| 17      | VRTN_OUT    | OR'd and Inrush protected VRTN Output Bus                                              |

| 18      | V_HLDP      | +ve terminal connection point for Holdup capacitor                                     |

\*\* Pins 10, 11 & 12 are present only on modules with I<sup>2</sup>C digital interface option (-K)

### **Feature Descriptions**

#### Introduction

The PIM400X module is designed to support the Advanced Telecommunications Computing Architecture (ATCA) power entry distribution requirements for the Front Board / Blade per the PICMG 3.0 specifications.

The PICMG 3.0 specification defines the Mechanical, Shelf Management Interface, Power Distribution, Thermal, Data I/O and Regulatory requirements for the next generation of modular telecom architecture platform for use in Central Office telecom environments.

#### **Input Pin Connections**

The ATCA board is specified to accept up to a maximum of 400W of input power via dual, redundant -48Vdc Feeds through the Zone 1 (Power and Management) connector, designated P10. The power connector provides board to backplane engagement via pins of varying lengths. Please consult the PICMG 3.0 specifications for details.

The following are the design considerations of the input pin connections of the PIM400X to the ATCA power connector.

| Fi<br>(P10 | rom ATCA<br>Connector) | Connection         | To PIM400X |                       |

|------------|------------------------|--------------------|------------|-----------------------|

| Pin<br>#   | Pin<br>Designation     | Requirement        | Pin<br>#   | Signal<br>Designation |

| 33         | -48V_A                 | Via Fuse(F3)       | 1          | -48V_AF               |

| 34         | -48V_B                 | Via Fuse(F4)       | 2          | -48V_BF               |

| 28         | VRTN_A                 | Via Fuse(F1)       | 3          | VRTN_AF               |

| 29         | VRTN_B                 | Via Fuse(F2)       | 4          | VRTN_BF               |

| 30         | EARLY_A                | Via Resistor(R1) * |            | -48V_A                |

| 31         | EARLY_B                | Via Resistor(R2) * |            | -48V_B                |

| 32         | ENABLE_A               | Via Fuse(F5)       | 5          | ENABLE_AF             |

| 27         | ENABLE_B               | Via Fuse(F6)       | 6          | ENABLE_BF             |

| 25         | SHELF_GND              | Direct             | 7          | SHELF_GND             |

| 26         | LOGIC_GND              | Direct             | 11         | LOGIC_GND             |

\* Pre-charge resistors

The first pins to mate in the ATCA power connector are the EARLY\_A, EARLY\_B, the two grounds (LOGIC\_GND, SHELF\_GND) and the two returns (VRTN\_A, VRTN\_B); followed by staggered connections of -48V\_A and -48V\_B power Feeds. The last pins to engage are the two short pins, ENABLE\_A & ENABLE\_B. The ATCA backplane connects the ENABLE\_A to VRTN\_A, ENABLE\_B to VRTN\_B, EARLY\_A to -48V\_A and EARLY\_B to -48V\_B. EARLY\_A & EARLY\_B Connections: During hot insertion of the ATCA board, the Inrush Control circuit limits the surge current to the C\_FLTR capacitor. However, due to the presence of a small amount of internal EMI filter capacitance (located before the Inrush Control circuit), it is recommended that Precharge resistors, R1 & R2 (100 Ohms, with appropriate surge capability) be connected as shown in the Typical Application circuit.

# Output Pin Connections (Standard Module: PIM400Z)

The output pin connections of the PIM400X to the system board are described below:

| Fro   | m PIM400X          | To ATC        | A Front Board      |                     |

|-------|--------------------|---------------|--------------------|---------------------|

| Pin # | Pin<br>Designation | Terminal      | Component          | Notes               |

| 15    | -48V_OUT           | Vin(-)        | DC/DC              | <i>(</i> <b>1</b> ) |

| 17    | VRTN_OUT           | Vin(+)        | DC/DC<br>Converter | (1)                 |

| 18    | V_HLDP             | +ve           | Holdup             | (2)                 |

| 16    | TRIM_HLDP          | RTrim         | Holdup             | (2)                 |

| 8     | +5V0               |               | Management         | (3)                 |

| 9     | +3V3               |               | Power              | (3)                 |

| 14    | ALARM              | $R_{pull-up}$ | IPM/System         | (4)                 |

# Additional Output Pin Connections (Modules with optional I<sup>2</sup>C Digital Interface: Option - K)

The following additional output pins of the PIM400KZ available for I<sup>2</sup>C Digital Interface to the IMP/System Controller are defined below:

|    |     | To ATCA Front Board<br>IPM/System Controller I2C<br>Interface | Notes |

|----|-----|---------------------------------------------------------------|-------|

| 10 | ADD | I2C Address w.r.t.<br>LOGIC_GND                               |       |

| 11 | DAT | I2C Data w.r.t. LOGIC_GND                                     | (5)   |

| 12 | CLK | I2C Clock w.r.t. LOGIC_GND                                    |       |

### Inrush Current Control / Hot Plug Functionality

The module provides inrush current control / hot plug capability. The peak value of the inrush current and the duration complies with the PICMG 3.0's Inrush Transient specifications. The specifications shall be met with the external C\_HLDP and C\_FLTR capacitances as specified in the previous sections. The unique design of the module where the large energy storage capacitors are segregated from the input filter capacitors allows the module to meet the stringent PICMG's inrush transient specifications with minimal energy storage capacitors.

### **Design Considerations**

#### -48V Main Output Bus: (Signal Names: -48V\_OUT & VRTN\_OUT)

This is the main -48V output bus that provides the payload power to the downstream (one or more) DC/ DC converters. The PIM400X module does not regulate or provide isolation from the input -48V A/B feeds.

The main functionality of the module is to provide - 48V A/B Feeds OR'ing, inrush protection for hot swap capability and EMI filtering to attenuate the noise generated by the downstream DC/DC converters.

- The -48V\_OUT pin connects to the Vin(-) pin and the VRTN\_OUT pin connects to the Vin(+) pin of the DC/DC converter (s).

- The -48V\_OUT bus may require a fuse depending on the power and fusing requirements of the DC/ DC converter.

- Input filtering of the DC/DC converter is provided by C\_FLTR close to the input pins of the DC/DC converter (s); additional high frequency decoupling ceramic capacitors (0.01 to 0.1µF are recommended for improved EMI performance.

- The maximum C\_FLTR capacitance across all the downstream DC/DC converters should not exceed 300µF.

- The minimum C\_FLTR capacitance (80µF) recommendation is based on meeting the EMI requirements.

### Holdup Capacitor Output Voltage (V\_HLDP)

This output provides the user settable high voltage to charge the C\_HLDP capacitor (s) to allow the ATCA board to meet the 5ms, 0Volts transient requirements.

- The V\_HLDP pin connects to the +ve terminals of the C\_HLDP capacitors while the –ve terminals of the C\_HLDP connects to the -48V\_OUT bus.

- The C\_HLDP capacitance is dependent on the system power and the holdup time requirements based on the following formula

$$C\_HLDP = \frac{2T_{HU}P_{HU}}{V\_HLDP^2 - V_{UV}^2}$$

Where  $T_{HU}$  is the desired holdup time,  $P_{HU}$  is the holdup power drawn from the holdup capacitors (=input power of the downstream DC/DC bus converter + Management Power), V\_HLDP is the trimmed holdup capacitor voltage and VUV is the undervoltage lockout threshold of either the

#### Holdup Capacitor Trim Voltage (TRM\_HLDP)

The resistor R\_TRIM sets the external holdup capacitor voltage to the desired setting. The output voltage is adjustable from 50 to 90V. The resistor, R\_TRIM is selected by the following equation:

$$R_TRIM(\Omega) = \left(\frac{500,000}{V_HLDP - 50.0} - 10,000\right)$$

#### High Voltage Discharge Mechanism:

Per the PICMG 3.0 specifications, the PIM400 provides an internal discharge mechanism to discharge the holdup/bulk capacitance to less than -60Vdc and less than 20 joules within one second of disconnection from the backplane.

#### Management Power (+3V3, +5V0)

Two isolated secondary output voltages (+3V3 & +5V0) are provided for ATCA Front Board's IPM/System Controller (3.3V) and for the Blue LED's (5.0V) power requirements. Both the outputs are referenced to LOGIC\_GND.

- The management power is available even when the input voltage is down to -36Vdc.

- No additional output capacitors are required, but a 22µF tantalum/ceramic and a 0.01 to 0.1µF ceramic capacitors are highly recommended to contain the switching ripple and noise.

### Input Fault Alarm Signal (ALARM)

Both the input feeds, -48V\_AF & -48\_BF are monitored via the -48V\_ALARM signal. In the event of a loss of power from either feeds (-48V\_A or -48V\_B) or the opening of their respective fuses, the -48V\_ALARM shall change its logical state indicating a fault. During normal operation, the signal is Low. During fault condition, the alarm signal shall assume a HI state when the ALARM pin is pulled up to an external pull voltage (maximum 5.0V) via an external pullup resistor (R<sub>Pullup</sub>). The ALARM output is internally referenced to the LOGIC\_GND. A 3.3K pull up resistor to 3.3V Management Power should suffice.

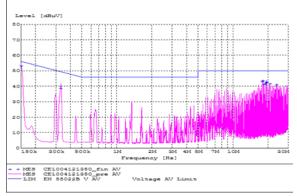

### **EMI Filtering**

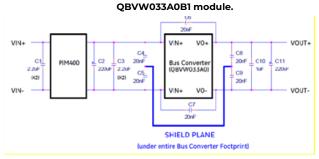

The module incorporates an EMI filter that is designed for the ATCA board to help meet the conducted emissions requirements of CISPR 22 Class B when used in conjunction with OmniOn's DC/DC bus converters recommended for ATCA applications. The following Figure 14 depicts the Class B EMI performance of PIM400F when tested with OmniOn's bus converter, QBVW033A0B1 with both modules mounted on the PIM400 Evaluation Board together with additional high frequency EMI capacitors (Fig 15).

Figure 14. Typical Class B EMC signature of PIM400F as tested with OmniOn's bus converter,

Figure 15. PIM400 & QBVW033A0 Bus Converter Test setup schematic

For Safety and noise considerations, copper traces must not be routed directly under the power module (PWB top layer). C\_EMI capacitors must make direct connections (preferably without vias) to the bus converter (DC/DC) module pins with as much copper width as possible. In case vias are necessary, allow for multiple connections to the inner plane with vias placed outside the footprint of the module. For additional layout guide-lines, refer to OmniOn's

FLT012A0Z Input Filter Module data sheet.

### **Safety Considerations**

For safety agency approval the power module must be installed in compliance with the spacing and separation requirements of the end-use safety agency standards, i.e., UL ANSI/UL\* 62368-1 and CAN/CSA+ C22.2 No. 62368-1 Recognized, DIN VDE 0868-1/ Al1:2017 (EN62368-1:2014/Al1:2017) The power input to these units is to be provided with a maximum of fast acting 20A fuses with a voltage rating of at least 75Vdc. Refer to "Thermal Consideration" section for additional safety considerations.

### **Thermal Considerations**

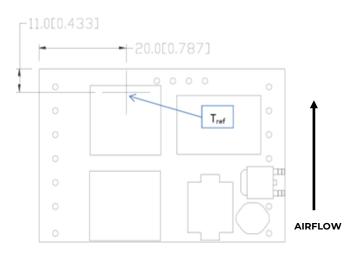

The power modules operate in a variety of thermal environments; however, sufficient cooling should be provided to help ensure reliable operation. Considerations include ambient temperature, airflow, module power dissipation, and the need for increased reliability. A reduction in the operating temperature of the module will result in an increase in reliability. The thermal data presented here is

based on physical measurements taken in a wind tunnel.

The thermal reference point, Tref, used in the specifications is shown in Figure 16. For reliable operation this temperature should not exceed 130°C. In addition, the output current of the module should not exceed the rated current for the module as listed in the Ordering Information table, or the derated current for the actual operating conditions as indicated in Figs. 17 & 18.

Figure 16. Tref Temperature Measurement Location.

### Heat Transfer via Convection

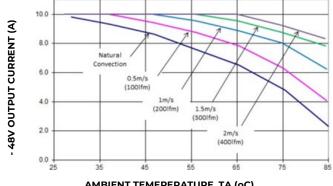

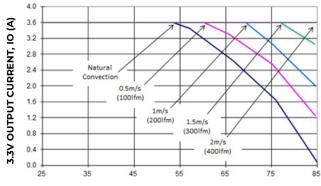

Increased airflow over the module enhances the heat transfer via convection. Derating curves showing the maximum output current that can be delivered by each module versus local ambient temperature (TA) for natural convection and up to 2 m/s (400 lfm) forced airflow are shown in Figures 17 & 18. Please refer to the Application Note "Thermal Characterization Process For Open-Frame Board-Mounted Power Modules" for a detailed discussion of thermal aspects including maximum device temperatures.

AMBIENT TEMEPERATURE, TA (oC)

Figure 17. -48V Output Current Derating for the Module; Airflow in the Transverse Direction from Pin7 to Pin1; Vin =48V & 3.3V @ 1.5A.

AMBIENT TEMEPERATURE, TA (oC)

Figure 18. 3.3V Output Current Derating for the Module: Airflow in the Transverse Direction from Pin7 to Pin1; Vin =48V & -48V Output current = 4A.

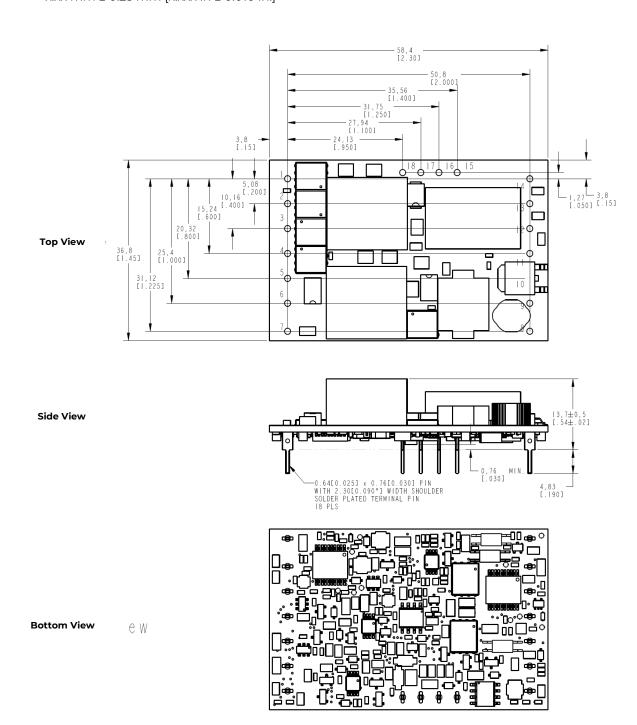

### Layout Considerations

The power modules are low profile in order to be used in fine pitch system card architectures. As such, component clearance between the bottom of the power module and the mounting board is limited. Avoid placing copper areas on the outer layer directly underneath the power module. Also avoid placing via interconnects underneath the power module. Particular attention should be paid to the clearance area as noted in the Bottom View of the Mechanical Outline drawing. For additional layout guidelines, refer to FLT012A0Z Data Sheet.

### Process Considerations

#### **Through-Hole Lead-Free Soldering Information**

The RoHS-compliant, Z version, through-hole products use the SAC (Sn/Ag/Cu) Pb-free solder and RoHScompliant components. The module is designed to be processed through single or dual wave soldering machines. The pins have a RoHS-compliant, pure tin finish that is compatible with both Pb and Pb-free wave soldering processes. A maximum preheat rate of 3°C/s is suggested. The wave preheat process should be such that the temperature of the power module board is kept below 210°C. For Pb solder, the recommended pot temperature is 260°C, while the Pb-free solder pot is 270°C max.

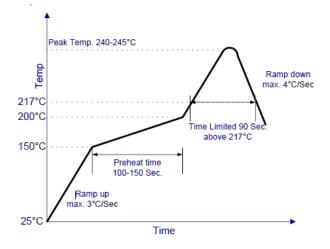

#### **Reflow Lead-Free Soldering Information**

The RoHS-compliant through-hole products can be processed with paste-through-hole Pb or Pb-free reflow process.

Max. sustain temperature : 245°C (J-STD-020C Table 4-2: Packaging Thickness>=2.5mm / Volume > 2000mm<sup>3</sup>).

Peak temperature over 245°C is not suggested due to the potential reliability risk of components under continuous high temperature.

Min. sustain duration above 217°C : 90 seconds Min. sustain duration above 180°C : 150 seconds

Max, heat up rate: 3°C/sec Max. cool down rate: 4°C/sec In compliance with JEDEC J-STD-020C spec for 2 times reflow requirement

#### **Pb-free Reflow Profile**

BMP module will comply with J-STD-020 Rev. C (Moisture/Reflow Sensitivity Classification for Nonhermetic Solid State Surface Mount Devices) for both Pb-free solder profiles and MSL classification procedures. BMP will comply with JEDEC J-STD-020C specification for 2 times reflow requirement. The suggested Pb-free solder paste is Sn/Ag/Cu (SAC). The recommended linear reflow profile using Sn/Ag/Cu solder is shown in Figure 19.

### **MSL** Rating

The modules have a MSL rating of 2a.

#### Storage and Handling

The recommended storage environment and handling procedures for moisture-sensitive surface mount packages is detailed in J-STD-033 Rev. A (Handling, Packing, Shipping and Use of Moisture/ Reflow Sensitive Surface Mount Devices). Moisture barrier bags (MBB) with desiccant are required for MSL ratings of 2 or greater. These sealed packages should not be broken until time of use. Once the original package is broken, the floor life of the product at conditions of  $\leq$  30°C and 60% relative humidity varies according to the MSL rating (see J-STD-033A). The shelf life for dry packed SMT packages will be a minimum of 12 months from the bag seal date, when stored at the following conditions: < 40° C, < 90% relative humidity.

Figure 19. Recommended linear reflow profile using Sn/Ag/Cu solder.

### Post Solder Cleaning and Drying Considerations

Post solder cleaning is usually the final circuit-board assembly process prior to electrical board testing. The result of inadequate cleaning and drying can affect both the reliability of a power module and the testability of the finished circuit-board assembly. For guidance on appropriate soldering, cleaning and drying procedures, refer to OmniOn Board Mounted Power Modules: Soldering and Cleaning Application Note (AP01-056EPS).

For additional information, please contact your Sales representative for more details.

### **Digital Feature Descriptions**

Full featured modules are available with I<sup>2</sup>C Digital Interface (Option -K).

Modules with I2C capability monitor up to five analog parameters and six status bits identified below in Tables 1and 2 respectively.

| Data_<br>pointer<br>value | Parameter   | Description                               | Scaling<br>Factor        |

|---------------------------|-------------|-------------------------------------------|--------------------------|

| 1eh                       | STATUS_BITS | Digital Signals<br>(See Table 2)          | N/A                      |

| 1Fh                       | V_HLDP      | Holdup voltage<br>w.r.t. –48_out          | 0.398 V/bits             |

| 21h                       | -48V_IOUT   | -48_out current                           | 0.094 A/bits             |

| 22h                       | -48V_AF     | Voltage between<br>-48V_AF and<br>VRTN_AF | 0.325 V/bits             |

| 23h                       | -48V_BF     | Voltage between<br>-48V_BF and<br>VRTN_BF | 0.325 V/bits             |

| 28h                       | TEMP        | Module<br>Temperature                     | (1.961° C/bit)<br>-50° C |

#### Table 1: Internal register memory map

| Bit | Name         | Description             | Value | Translation                       |

|-----|--------------|-------------------------|-------|-----------------------------------|

| 0   | ENABLE_AF_ST | ENABLE_AF_              | 0     | ENABLE_AF IS<br>Disabled          |

|     | ATUS         | Signal Status           | 1     | ENABLE_AF IS<br>Enabled           |

| 1   | ENABLE_BF_ST | ENABLE_BF_              | 0     | ENABLE_BF IS<br>Disabled          |

|     | ATUS         | Signal Status           | 1     | ENABLE_BF IS<br>Enabled           |

| 2   | ALRAM STATUS | ALARM                   | 0     | ALARM not set                     |

| 2   | ALRAM_STATUS | signal status           | 1     | ALARM is set                      |

| 3   | N/A          | Reserved                |       |                                   |

| ,   |              | Holdup<br>status        | 0     | C_HLDP not<br>connected           |

| 4   | 4 HLDP_STAUS |                         | 1     | C_HLDP is<br>connected            |

| _   | HOTSWAP      | Holdup                  | 0     | Hot swap<br>switch is off         |

| 5   | STATUS       | status                  | 1     | Hot swap<br>switch is on          |

| 6   | -48VOUT_     | -48v_OUT<br>Undervoltag | 0     | -48V_OUT is<br>below<br>threshold |

| Ø   | STATUS       | e alarm<br>status       | 1     | -48V_OUT is<br>above<br>threshold |

| 7   | N/A          | Reserved                |       |                                   |

Table 2: Digital signals

Note: Bit 0=LSB, Bit 7=MSB

### I<sup>2</sup>C Command Structure:

The I<sup>2</sup>C is a 2-wire interface supporting multiple devices and masters on a single bus. The connected devices can only pull the bus wires low and they never drive the bus high. The bus wires should be externally connected to a positive supply voltage via a pull-up resistor. When the bus is idle, both DAT and CLK are high. The max sink current supported on the I2C bus is 3.5mA.

Each device on the I<sup>2</sup>C bus is recognized by a unique address stored in that device. Devices can be classified as masters or slaves when performing data transfers. A master is a device which initiates a data transfer on the bus and generates clock signals to permit that transfer. At the same time, any device addressed is considered slave. The PIM400 always acts as a slave.

In PIM400 module, I<sup>2</sup>C interface is used for reporting critical parameters like input voltage, output current, holdup capacitor voltage and temperature data. The read protocol is shown in the Fig 20 below.

#### Fig 20: Typical I<sup>2</sup>C Read protocol

#### Address Structure:

7 bit Address + R/W bit

Four bits are fixed (0101), three bits (xyz) are variable,

|                                                      | 8 bit Address |     |

|------------------------------------------------------|---------------|-----|

| 0101                                                 | xyz*          | R/W |

| and the least Table 3: Address structure significant |               |     |

and the leastbit is the read/ significant write bit.

### Address Selection:

The three bits (xyz) of the address are set with a single external resistor from the ADD (pin10) to LOGIC\_GND (pin 13). The 8 possible addresses are shown in Table 4 with the respective resistance values.

| Address For write<br>( R/W = 0) | Xyz from<br>Table 3 | R(Ω)   |

|---------------------------------|---------------------|--------|

| 5 Eh                            | 111                 | Open   |

| 5 Ch                            | 110                 | 100000 |

| 5 Ah                            | 101                 | 40200  |

| 58 h                            | 100                 | 20000  |

| 56h                             | 011                 | 10000  |

| 54h                             | 010                 | 4020   |

| 52h                             | 001                 | 2000   |

| 50h                             | 000                 | Short  |

Table 4: I<sup>2</sup> C Addressing

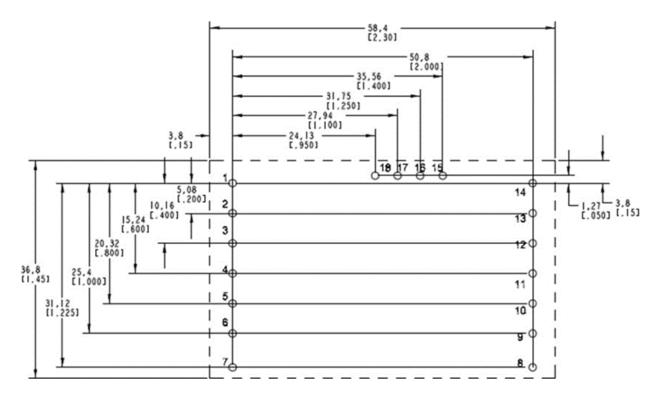

### **Mechanical Outline**

Dimensions are in millimeters and [inches]. Tolerances: x.x mm  $\pm$  0.5 mm [x.xx in.  $\pm$  0.02 in.] (unless otherwise indicated) x.xx mm  $\pm$  0.25 mm [x.xxx in  $\pm$  0.010 in.]

### **Recommended Pad Layout**

Dimensions are in and millimeters [inches].

Tolerances: x.x mm ± 0.5 mm [x.xx in. ± 0.02 in.] (unless otherwise indicated)

x.xx mm ± 0.25 mm [x.xxx in ± 0.010 in.]

| Pin No. | Signal Name | Pin No. | Signal Name |

|---------|-------------|---------|-------------|

| 1       | -48V_AF     | 10**    | ADD         |

| 2       | -48V_BF     | 11**    | DAT         |

| 3       | VRTN_AF     | 12**    | CLK         |

| 4       | VRTN_BF     | 13      | LOGIC_GND   |

| 5       | ENABLE_AF   | 14      | ALARM       |

| 6       | ENABLE_BF   | 15      | -48V_OUT    |

| 7       | SHELF_GND   | 16      | TRIM_HLDP   |

| 8       | +5V0        | 17      | VRTN_OUT    |

| 9       | +3V3        | 18      | V_HLDP      |

\*\* Pins 10, 11 & 12 are present only on modules with I<sup>2</sup> C digital interface option (-K).

#### NOTES: 1. FOR 0.030" X 0.025" RECTANGULAR PIN, USE 0.050" PLATED THROUGH HOLE

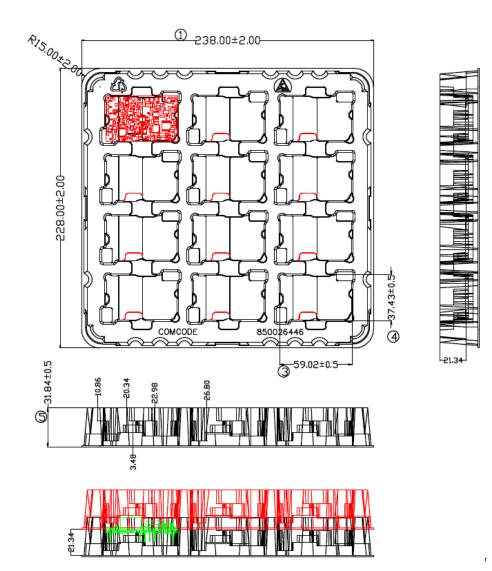

### **Packaging Details**

The modules are supplied as standard in the plastic trays shown in Figure below.

### **Tray Specification**

| Material                | Antistatic coated PVC                             |

|-------------------------|---------------------------------------------------|

| Max surface resistivity | 10 <sup>12</sup> Ω/sq                             |

| Color                   | Clear                                             |

| Capacity                | 12 power modules                                  |

| Min order quantity      | 24 pcs (1 box of 2 full trays + 1 empty top tray) |

Each tray contains a total of 12 power modules. The trays are self-stacking and each shipping box for the modules will contain 2 full trays plus 1 empty hold down tray giving a total number of 24 power modules.

#### Notes:

- 1. All radius unspecified are R2.0mm

- 2. All angle unspecified are 5°

- 3. Dimension unit: mm (L); A<sup>o</sup>(A).

### **Ordering Information**

Please contact your OmniOn Sales Representative for pricing, availability and optional features

| Input Voltage  | Current<br>Rating | Auxiliary<br>Output #1 | Auxiliary<br>Output #2 | Options                                                     | Product codes | Ordering<br>Codes |

|----------------|-------------------|------------------------|------------------------|-------------------------------------------------------------|---------------|-------------------|

| -36 to -75 Vdc | 10A               | 3.3V/3.6A              | 5.0V/0.15A             | -                                                           | PIM400Z       | 150019196         |

| -36 to -75 Vdc | 10A               | 3.3V/3.6A              | 5.0V/0.15A             | I <sup>2</sup> C Digital Interface                          | PIM400KZ      | 150019197         |

| -36 to -75 Vdc | 10A               | 3.3V/3.6A              | 5.0V/0.15A             | I <sup>2</sup> C Digital Interface & Short<br>pins (3.68mm) | PIM400K6Z     | 150033384         |

Table 1. Device Code

| Option                                              | Device Code Suffix |

|-----------------------------------------------------|--------------------|

| Short pins: 3.68mm ± 0.25mm (0.145 in. ± 0.010 in.) | 6                  |

| Short pins: 2.79mm ± 0.25mm (0.110 in. ± 0.010 in.) | 8                  |

| I <sup>2</sup> C Digital Interface                  | К                  |

#### **Table 2. Device Options**

| Description                                                                                                                        | Product Code  | Ordering Codes |

|------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|

| PIM400 Evaluation Board                                                                                                            | EVAL_PIM400   | 150030502      |

| QBDW033A0B Series Power Modules; DC-DC Converters36-75V <sub>dc</sub> Input;<br>8.1-13.2V <sub>dc</sub> Output; 33A Output Current | QBDW033A0B41Z | CC109159307    |

| QBVW033A0B Series Power Modules; DC-DC Converters36-75V <sub>dc</sub> Input;<br>8.1-13.2V <sub>dc</sub> Output; 33A Output Current | QBVW033A0B41Z | CC109165247    |

Table 3. Related Products

# Change History (excludes grammar & clarifications)

| Revision | Date       | Description of the change         |

|----------|------------|-----------------------------------|

| 11.4     | 05/10/2022 | Updated format RoHs Standard      |

| 11.5     | 06/24/2022 | Updated external cap rating typos |

| 11.6     | 11/21/2023 | Updated as per OmniOn template    |

### **OmniOn Power Inc.**

601 Shiloh Rd. Plano, TX USA

### omnionpower.com

We reserve the right to make technical changes or modify the contents of this document without prior notice. OmniOn Power does not accept any responsibility for errors or lack of information in this document and makes no warranty with respect to and assumes no liability as a result of any use of information in this document. We reserve all rights in this document and in the subject matter and illustrations contained therein. Any reproduction, disclosure to third parties or utilization of its contents – in whole or in parts – is forbidden without prior written consent of OmniOn Power. This document does not convey license to any patent or any intellectual property right. Copyright© 2023 OmniOn Power Inc. All rights reserved.